**Features**

# Dual, 10-Bit, Current-Sink Output DAC

### **General Description**

The MAX5547 dual, 10-bit, dual range, digital-to-analog converter (DAC) sinks up to 3.6mA of current, making it ideal for laser-driver-control applications. Parallel the MAX5547 outputs to sink higher current (up to 7.2mA max). Operating from a single +2.7V to +5.25V supply, the MAX5547 typically consumes 1mA (internal reference).

The MAX5547 operates from a precision +2.5V internal 4ppm/°C reference or an external reference in the +2.45V to +2.55V range. The maximum full-scale current-sink range is software programmable to 3.6mA or 1.2mA for each DAC. A 10MHz SPI™-compatible serial interface configures the device.

The MAX5547 is available in a 3mm x 3mm x 0.8mm 8pin TDFN package and is specified over the -40°C to +85°C extended temperature range.

### **Applications**

Laser-Driver Control Pin-Diode Bias Currents Modulation Currents Average Power

**Extinction Ratios**

### **Dual Current-Sink DACs**

- 10-Bit Resolution

- Two Software-Programmable Full-Scale Current Ranges: 3.6mA or 1.2mA

- ◆ Parallelable Outputs for Up to 7.2mA (max)

- ♦ +2.5V Internal Reference Drifts Only 4ppm/°C

- ♦ +2.7V to +5.25V Single-Supply Operation

- ♦ INL: ±4 LSB (1.2mA Output)

- ♦ DNL: ±0.75 LSB (Guaranteed Monotonic)

- ♦ Low +0.8V Output Compliance

- ♦ Ultra-Small, 3mm x 3mm x 0.8mm, 8-Pin TDFN **Package**

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-<br>PACKAGE | TOP<br>MARK | PKG<br>CODE |

|------------|----------------|-----------------|-------------|-------------|

| MAX5547ETA | -40°C to +85°C | 8 TDFN-EP*      | APF         | T833-2      |

<sup>\*</sup>EP = Exposed pad.

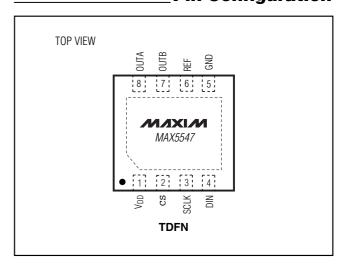

Pin Configuration appears at end of data sheet.

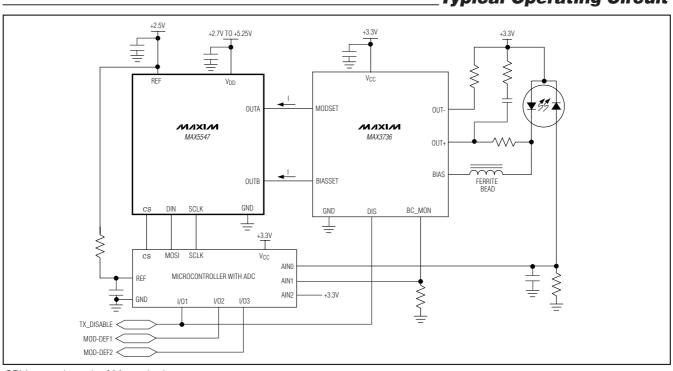

## Typical Operating Circuit

SPI is a trademark of Motorola, Inc.

MIXIM

### **ABSOLUTE MAXIMUM RATINGS**

| $V_{DD}$ to GND0.3V to +6V OUTA, OUTB, REF to GND0.3V to ( $V_{DD}$ + 0.3V) SCLK, DIN, $\overline{CS}$ to GND0.3V to +6V Continuous Power Dissipation ( $T_A = +70^{\circ}\text{C}$ )  8-Pin TDFN (denate 18 2mW/°C above +70°C) 1454 5mW | Operating Temperature Range40°C to +85°C  Junction Temperature+150°C  Storage Temperature Range65°C to +150°C  Lead Temperature (soldering, 10s)+300°C |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8-Pin TDFN (derate 18.2mW/°C above +70°C)1454.5mW                                                                                                                                                                                         |                                                                                                                                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7 \text{ to } +5.25 \text{V}, \text{ GND} = 0, \text{ external reference} = +2.5 \text{V}, \text{ output voltage} = +2.0 \text{V}, T_{A} = -40 ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ . Typical values are at  $V_{DD} = +3.0 \text{V}, \text{ and } T_{A} = +25 ^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                     | SYMBOL           | COND                                | MIN                | TYP  | MAX  | UNITS   |                   |  |

|-----------------------------------------------|------------------|-------------------------------------|--------------------|------|------|---------|-------------------|--|

| STATIC PERFORMANCE—ANAI                       | OG SECTIO        | N                                   |                    |      |      |         |                   |  |

| Resolution                                    |                  |                                     |                    | 10   |      |         | Bits              |  |

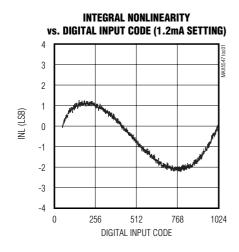

| Integral Naplinearity (Nata 2)                | INL              | $I_{OUT} = 1.2mA$                   |                    |      |      | ±4      | LSB               |  |

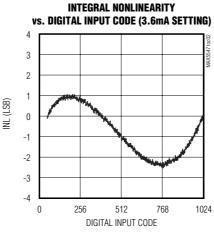

| Integral Nonlinearity (Note 2)                | IINL             | $I_{OUT} = 3.6 \text{mA}$           |                    |      |      | ±6      | LOD               |  |

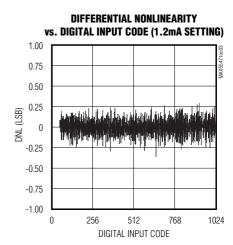

| Differential Nonlinearity                     | DNL              | Guaranteed monotoni                 | ic                 |      |      | ±0.75   | LSB               |  |

| Offset Error                                  | OE               | Code = 030h                         |                    |      | ±4   |         | LSB               |  |

| Offset Temperature Coefficent                 |                  |                                     |                    |      | 0.05 |         | LSB/°C            |  |

| Gain Error                                    | GE               | Measured from code                  | $I_{OUT} = 1.2mA$  |      | ±0.1 | ±3      | %                 |  |

| daiii Eiroi                                   | GL.              | 030h to 3FFh                        | $I_{OUT} = 3.6mA$  |      | ±0.1 | ±5.5    | /0                |  |

| Gain Temperature Coefficient                  |                  | I <sub>OUT</sub> _ = 1.2mA          |                    |      | 15   |         | ppm/°C            |  |

| dain reinperature Coefficient                 |                  | $I_{OUT} = 3.6mA$                   |                    | 25   |      | ррпі, С |                   |  |

| Line Regulation                               |                  | $V_{DD} = +2.7V \text{ to } +5.25$  |                    |      | 0.8  | LSB/V   |                   |  |

| Output Crosstalk                              |                  | OUTA = midscale, OU<br>030h to 3FFh | JTB switching from |      | 54   |         | dB                |  |

| REFERENCE                                     | •                | •                                   |                    | •    |      |         | •                 |  |

| Internal-Reference Voltage                    | V <sub>REF</sub> | T <sub>A</sub> = +25°C              |                    | 2.48 | 2.5  | 2.52    | V                 |  |

| Internal-Reference Temperature<br>Coefficient |                  | (Note 3)                            |                    |      | 4    | 35      | ppm/°C            |  |

| Internal-Reference Load<br>Regulation         |                  | 0μA < I <sub>REF</sub> < +300μA     |                    |      | 1    | 3.5     | Ω                 |  |

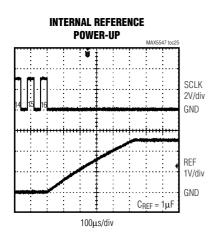

| Internal-Reference Power-Up<br>Time           |                  | $C_{REF} = 1\mu F$ , to 0.05%       |                    |      | 0.55 |         | ms                |  |

| Internal-Reference Sink Current               |                  |                                     |                    |      |      | 50      | μΑ                |  |

| Internal-Reference Source<br>Current          |                  |                                     |                    |      |      | 300     | μA                |  |

| REF Capacitive Load                           |                  | (Note 3)                            |                    | 0.1  |      | 10.0    | μF                |  |

| Reference Line Regulation                     |                  | $V_{DD} = +2.7V \text{ to } +5.25$  | ١V                 |      | 25   |         | μV/V              |  |

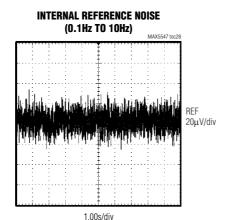

|                                               |                  | f = 0.1Hz to 10Hz                   |                    |      | 10   |         | μV <sub>RMS</sub> |  |

| Internal-Reference Noise                      |                  | f = 10Hz to 10kHz                   |                    |      | 27   |         |                   |  |

| External-Reference Range                      | V <sub>REF</sub> |                                     |                    | 2.45 |      | 2.55    | V                 |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7 \text{ to } +5.25 \text{V}, \text{ GND} = 0, \text{ external reference} = +2.5 \text{V}, \text{ output voltage} = +2.0 \text{V}, T_{A} = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ . Typical values are at  $V_{DD} = +3.0 \text{V}, \text{ and } T_{A} = +25 ^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                  | SYMBOL                            | MIN                                                    | TYP                        | MAX   | UNITS                     |       |                    |

|--------------------------------------------|-----------------------------------|--------------------------------------------------------|----------------------------|-------|---------------------------|-------|--------------------|

| External-Reference Input Impedance         | R <sub>REF</sub>                  |                                                        |                            |       | 90                        |       | kΩ                 |

| DAC OUTPUTS                                | <b>II</b>                         | •                                                      |                            | I.    |                           |       |                    |

|                                            |                                   | 1.2mA low-current range                                | Code = 030h<br>Code = 3FFh | 1170  | 50<br>1200                | 1230  |                    |

| Output Current (Note 4)                    | IOUT_                             | 3.6mA high-current range                               | Code = 030h<br>Code = 3FFh | 3400  | 150<br>3600               | 3800  | μΑ                 |

| LSB Size                                   |                                   | 1.2mA full-scale current 3.6mA full-scale current      | I .                        | 0.100 | 1.17<br>3.52              |       | μΑ                 |

| Current-Source Compliance<br>Voltage Range |                                   | I <sub>OUT</sub> = full-scale (Note                    | 0.8                        |       | V <sub>DD</sub>           | V     |                    |

| Output Impedance at Full-Scale<br>Current  |                                   | $I_{OUT} = 1.2 \text{mA}$<br>$I_{OUT} = 3.6 \text{mA}$ |                            |       | 800<br>180                |       | kΩ                 |

| DYNAMIC PERFORMANCE                        |                                   |                                                        |                            |       |                           |       |                    |

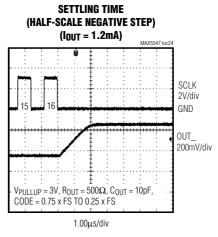

| Settling Time                              | ts                                | To 1% (Note 6)                                         |                            |       | 10                        |       | μs                 |

| Output Noise                               | I <sub>RMS</sub>                  | f = 0.1Hz to $10Hzf = 10Hz$ to $10kHz$                 |                            |       | 0.05<br>0.35              |       | LSB <sub>RMS</sub> |

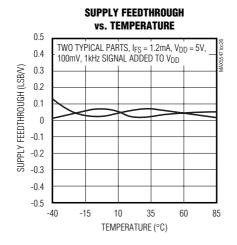

| Supply Feedthrough                         |                                   | 100mV, 1kHz signal add                                 | ded to Vnn                 |       | 0.85                      |       | LSB/V              |

| Digital Feedthrough                        |                                   | $R_{LOAD} = 500\Omega$ , $C_{LOAD}$ :                  |                            |       | 2                         |       | pA•s               |

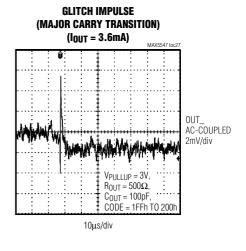

| Digital-to-Analog Glitch Impulse           |                                   | $R_{LOAD} = 500\Omega$ , $C_{LOAD}$ :                  |                            |       | 16                        |       | pA•s               |

| DAC-to-DAC Full-Scale Current<br>Matching  |                                   |                                                        | ·                          |       | 2                         |       | %                  |

| POWER SUPPLIES                             | ·I                                |                                                        |                            | I.    |                           |       |                    |

| Supply Voltage                             | $V_{DD}$                          |                                                        |                            | +2.70 |                           | +5.25 | V                  |

| Supply Current                             | lnn                               | V <sub>DD</sub> = +5.25V, no load,                     | Internal reference mode    |       | 1.1                       | 2     | - mA               |

| оприу Сипені                               | pply Current IDD SCLK not switchi |                                                        | External reference mode    |       | 0.75 1.5                  |       | IIIA               |

| LOGIC AND CONTROL INPUTS                   | T                                 | 1                                                      |                            | ı     |                           |       | ,                  |

| Input High Voltage                         | V <sub>IH</sub>                   | (Note 7)                                               | 0.7 x<br>V <sub>DD</sub>   |       |                           | V     |                    |

| Input Low Voltage                          | VIL                               | (Note 7)                                               |                            |       | 0.8                       | V     |                    |

| Input Hysteresis                           | V <sub>HYS</sub>                  |                                                        |                            |       | 0.05 x<br>V <sub>DD</sub> |       | V                  |

| Input Capacitance                          | C <sub>IN</sub>                   |                                                        |                            |       | 10                        |       | рF                 |

| Input Leakage Current                      | I <sub>IN</sub>                   |                                                        |                            |       |                           | ±1    | μΑ                 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7 \text{ to } +5.25\text{V}, \text{ GND} = 0, \text{ external reference} = +2.5\text{V}, \text{ output voltage} = +2.0\text{V}, T_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}.$  Typical values are at  $V_{DD} = +3.0\text{V}, \text{ and } T_{A} = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                       | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------------|-----------------|------------|-----|-----|-----|-------|

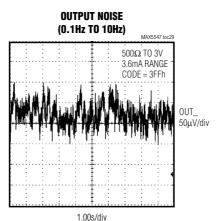

| SPI TIMING CHARACTERISTICS      | (see Figure 1)  |            |     |     |     |       |

| SCLK Clock Period               | t <sub>CP</sub> |            | 100 |     |     | ns    |

| SCLK Pulse-Width High           | tсн             |            | 40  |     |     | ns    |

| SCLK Pulse-Width Low            | tCL             |            | 40  |     |     | ns    |

| CS Fall to SCLK Fall Setup Time | tcss            |            | 25  |     |     | ns    |

| SCLK Fall to CS Rise Hold Time  | tcsh            |            | 50  |     |     | ns    |

| DIN to SCLK Fall Setup Time     | t <sub>DS</sub> |            | 40  |     |     | ns    |

| DIN to SCLK Fall Hold Time      | tDH             |            | 0   |     |     | ns    |

| CS Pulse-Width High             | tcsw            |            | 100 |     |     | ns    |

- Note 1: Devices are 100% production tested at  $T_A = +25$ °C. Limits over temperature are guaranteed by design.

- Note 2: INL linearity is from code 48 to code 1023.

- Note 3: Guaranteed by design. Not production tested.

- Note 4: The DACs continue to operate at currents lower than 50μA on the 1.2mA range and 150μA on the 3.6mA range. However, performance is not guaranteed at these low currents. A code of all zeros has a nominal output current of 0μA.

- Note 5: Compliance voltage range is defined as the range where the output current is -2 LSB of its value at  $V_{OUT} = +1V$ .

- **Note 6:** Settling time is measured from 0.25 x full scale to 0.75 x full scale.

- Note 7: The device draws higher supply current when the digital inputs are driven with voltages between (V<sub>DD</sub> 0.5V) and (GND + 0.5V). See Supply Current vs. Digital Input Voltage in the *Typical Operating Characteristics*.

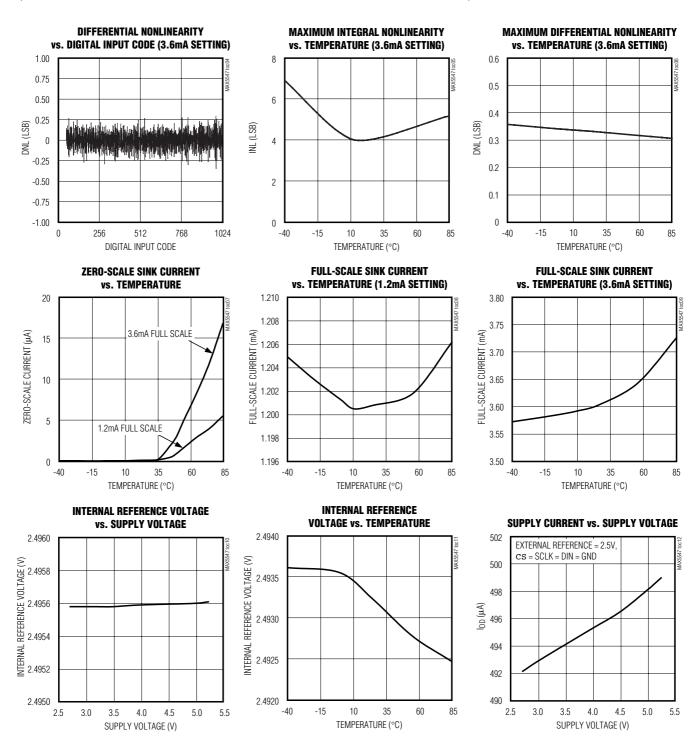

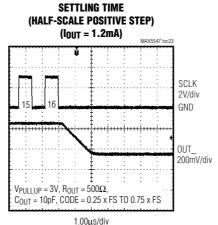

### Typical Operating Characteristics

$(V_{DD} = +3.0V, GND = 0, external reference = +2.5V, T_A = +25$ °C, unless otherwise noted.)

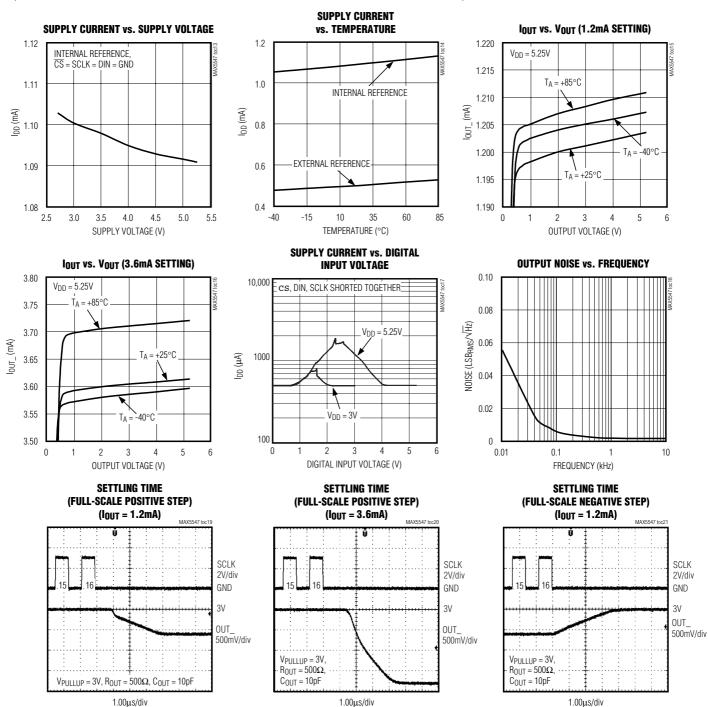

## Typical Operating Characteristics (continued)

$(V_{DD} = +3.0V, GND = 0, external reference = +2.5V, T_A = +25^{\circ}C, unless otherwise noted.)$

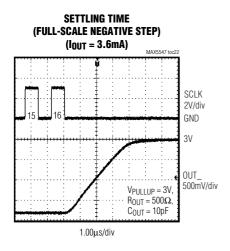

## Typical Operating Characteristics (continued)

$(V_{DD} = +3.0V, GND = 0, external reference = +2.5V, T_A = +25^{\circ}C, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

$(V_{DD} = +3.0V, GND = 0, external reference = +2.5V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                           |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>DD</sub> | Supply Voltage. Set V <sub>DD</sub> between +2.7V to +5.25V. Bypass V <sub>DD</sub> with a 0.1µF capacitor to GND, as close to the device as possible.                                                                                                                                                             |

| 2   | CS              | Active-Low Chip-Select Input. Set $\overline{\text{CS}}$ low to enable the serial interface.                                                                                                                                                                                                                       |

| 3   | SCLK            | Serial-Clock Input                                                                                                                                                                                                                                                                                                 |

| 4   | DIN             | Serial-Data Input. DIN is clocked into the serial interface on the falling edge of SCLK.                                                                                                                                                                                                                           |

| 5   | GND             | Ground                                                                                                                                                                                                                                                                                                             |

| 6   | REF             | External Reference Input/Internal Reference Output. When programmed for internal reference mode, REF is a +2.5V output. When programmed for external reference mode, apply a voltage between +2.45V and +2.55V (see Table 1). Connect a 1µF ceramic capacitor from REF to GND, as close to the device as possible. |

| 7   | OUTB            | DAC B Current Output. OUTB sinks up to 3.6mA.                                                                                                                                                                                                                                                                      |

| 8   | OUTA            | DAC A Current Output. OUTA sinks up to 3.6mA.                                                                                                                                                                                                                                                                      |

| _   | EP              | Exposed Pad. Connect to GND. Do not use as the ground connection.                                                                                                                                                                                                                                                  |

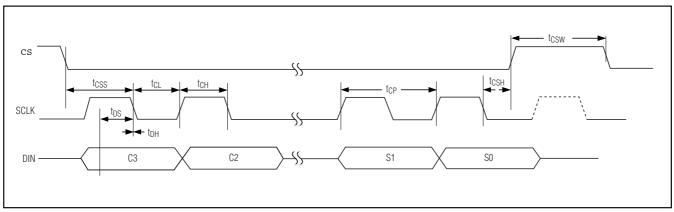

### **Detailed Description**

The MAX5547 10-bit, dual-range, current-sink DAC operates with serial data clock rates up to 10MHz. The double-buffered DAC input consists of a 16-bit input register and two 10-bit DAC registers, followed by a current-steering array (see the *Functional Diagram*). The MAX5547 sinks full-scale output currents of 1.2mA or 3.6mA per DAC. Each DAC's full-scale current can be independently programmed.

Operating from a single +2.7V to +5.25V supply, the MAX5547 typically consumes 1mA. The MAX5547 operates from an internal +2.5V reference or an external reference in the +2.45V to +2.55V range.

The MAX5547 is ideal as the digital/analog interface for laser-diode drivers with current-controlled inputs, such as the MAX3736 (see the *Typical Operating Circuit*). Set the current levels at the MAX3736's MODSET and BIASSET current-controlled inputs from the MAX5547's DAC outputs. The MAX3736's MODSET and BIASSET lines set the laser driver's desired modulation and bias currents.

#### **Reference Architecture and Operation**

The MAX5547 operates from an internal +2.5V reference or accepts an external reference voltage source between +2.45V and +2.55V. The internal reference is capable of sinking up to  $50\mu A$  and sourcing up to  $300\mu A$ . REF serves as the input for a low-impedance

reference source in external reference mode. Bypass REF to GND with a ceramic capacitor in the 0.1µF to 10µF range, as close to the device as possible, in both internal and external reference modes.

During startup, when power is first applied, the MAX5547 defaults to external reference mode, and to the 1.2mA full-scale current-range mode. Use software commands to select internal reference mode and 3.6mA full-scale current-range mode (see Table 1).

#### DAC Data

The MAX5547's internal registers set the DAC full-scale output currents (IFS) to 1.2mA or 3.6mA (see Table 1). The 10-bit DAC data is decoded as straight binary, with 1 LSB = IFS / 1023, and converted into the corresponding current as shown in Table 2.

### Serial Interface

The MAX5547 operates through a 3-wire, 10MHz SPI-compatible serial interface.  $\overline{CS}$ , SCLK, and DIN control the serial interface timing and data. Ensure the SPI bus master, typically a microcontroller ( $\mu$ C), runs in master mode so that it generates the serial clock signal. Select an SCLK frequency of 10MHz or less and set the clock polarity (CPOL) and phase (CPHA) in the  $\mu$ C control registers to opposite values. The MAX5547 operates with SCLK idling high or low. Therefore, set CPOL = 0 and CPHA = 1, or CPOL = 1 and CPHA = 0.

Figure 1. SPI Serial-Interface Timing Diagram

Set  $\overline{\text{CS}}$  low to begin clocking input data at DIN on the falling edge of SCLK (see Figure 1). Serial communications to the shift register consist of a 16-bit command word loaded from DIN. The first four control bits (C3–C0) determine the target register (see Table 1). The next 10 data bits set the current-sink level. D9 is the MSB and D0 the LSB. Set bits S1 and S0 to zero for proper operation. Data is latched into the appropriate DAC register on the 16th SCLK falling edge. After writing 16 bits, drive  $\overline{\text{CS}}$  high. Keep  $\overline{\text{CS}}$  low throughout the entire 16-bit word.

Write the command word to configure DAC registers A and B individually or both registers at the same time. The command word also determines whether the DACs use the internal or external reference.

The MAX5547 powers up in external reference mode with DAC registers A and B set to IFS = 1.2mA at code 000h.

### Applications Information

### **Power Sequencing**

Ensure the voltages applied at REF, OUTA, and OUTB do not exceed VDD at any time. If proper power sequencing is not possible, connect an external Schottky diode between REF/OUTA/OUTB and VDD to ensure compliance with the absolute maximum ratings.

# Power-Supply Bypassing and Ground Management

Digital or AC transient signals on GND create noise at the analog output. Return GND to the highest quality ground plane available. For extremely noisy environments, bypass both REF and  $V_{DD}$  to GND with  $10\mu F$  and  $0.1\mu F$  capacitors in parallel, with the  $0.1\mu F$  capacitor as close to the device as possible. Careful PC board ground layout minimizes crosstalk between the DAC outputs and digital inputs.

**Table 1. Command Word Summary**

| C  | ONTR | OL BI | TS | MSB         |                     |                                                                                            |             | DAT   | A BITS | 3                                                                                           |                                                                                                |    | LSB                                                                      |                                                                          |    | REGISTER FUNCTION                                                                                         |

|----|------|-------|----|-------------|---------------------|--------------------------------------------------------------------------------------------|-------------|-------|--------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------|--------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------------------------------|

| СЗ | C2   | C1    | C0 | D9          | D8                  | D7                                                                                         | D6          | D5    | D4     | D3                                                                                          | D2                                                                                             | D1 | D0                                                                       | S1                                                                       | S0 |                                                                                                           |

| 0  | 0    | 0     | 0  | X           | X                   | X                                                                                          | X           | X     | X      | X                                                                                           | X                                                                                              | X  | X                                                                        | 0                                                                        | 0  | External reference mode (default state). Connect an external voltage source at REF from +2.45V to +2.55V. |

| 1  | 0    | 0     | 0  | Х           | Χ                   | Х                                                                                          | X           | X     | Х      | Х                                                                                           | Χ                                                                                              | Χ  | X                                                                        | 0                                                                        | 0  | Internal reference mode. Internal reference is +2.5V.                                                     |

| 0  | 0    | 1     | 0  |             |                     |                                                                                            |             | 10-bi | t data |                                                                                             |                                                                                                |    |                                                                          | 0                                                                        | 0  | Load DAC register A and set I <sub>OUTA</sub> full-scale range to 1.2mA.                                  |

| 0  | 0    | 1     | 1  |             |                     |                                                                                            | x x x x x   |       |        |                                                                                             |                                                                                                | 0  | 0                                                                        | Load DAC register A and set I <sub>OUTA</sub> full-scale range to 3.6mA. |    |                                                                                                           |

| 0  | 1    | 0     | 0  |             |                     | 10-bit data  10-bit data  10-bit data                                                      |             |       |        |                                                                                             |                                                                                                | 0  | 0                                                                        | Load DAC register B and set I <sub>OUTB</sub> full-scale range to 1.2mA. |    |                                                                                                           |

| 0  | 1    | 0     | 1  |             |                     | D7 D6 D5 D4 D3  X X X X X X  X X X X X  10-bit data  10-bit data  10-bit data  10-bit data |             |       |        |                                                                                             | 0                                                                                              | 0  | Load DAC register B and set I <sub>OUTB</sub> full-scale range to 3.6mA. |                                                                          |    |                                                                                                           |

| 0  | 1    | 1     | 0  | 10-bit data |                     |                                                                                            |             |       | 0      | 0                                                                                           | Load DAC registers A and B and set IOUTA and IOUTB full-scale ranges to 1.2mA (default state). |    |                                                                          |                                                                          |    |                                                                                                           |

| 0  | 1    | 1     | 1  |             | 10-bit data 0 0 set |                                                                                            | 10-bit data |       |        | Load DAC registers A and B and set I <sub>OUTA</sub> and I <sub>OUTB</sub> ranges to 3.6mA. |                                                                                                |    |                                                                          |                                                                          |    |                                                                                                           |

X = Don't care. Unused codes are reserved for factory use.

## **Table 2. Ideal DAC Output Code Table**

| BINARY DAC CODE | I <sub>OUT</sub> _            |

|-----------------|-------------------------------|

| 11 1111 1111    | 1023×  FS  <br>1023           |

| 10 0000 0000    | 512×  FS<br>1023              |

| 00 0000 0001    | <u>I<sub>FS</sub></u><br>1023 |

| 00 0000 0000    | 0                             |

## **Chip Information**

PROCESS: BiCMOS

10 \_\_\_\_\_\_\_ **/V**|/|X|/V

## Functional Diagram

## **Pin Configuration**

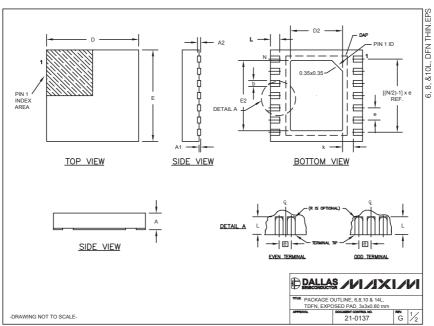

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

|                           |                                                                     |                                                                                         |                                                  |            |                  |           |               |             | 21-0137                                      | G           |

|---------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------|------------|------------------|-----------|---------------|-------------|----------------------------------------------|-------------|

|                           |                                                                     |                                                                                         |                                                  |            |                  |           |               |             |                                              |             |

|                           |                                                                     |                                                                                         |                                                  |            |                  |           |               |             |                                              |             |

| COM                       | IMON DIME                                                           | NSIONS                                                                                  | 1                                                |            |                  |           |               |             |                                              |             |

| SYMBO                     |                                                                     | MAX                                                                                     | -                                                |            |                  |           |               |             |                                              |             |

| A                         | 0.70                                                                | 0.80                                                                                    | 1                                                |            |                  |           |               |             |                                              |             |

| D                         | 2.90                                                                | 3.10                                                                                    | 1                                                |            |                  |           |               |             |                                              |             |

| E                         | 2.90                                                                | 3.10                                                                                    | ]                                                |            |                  |           |               |             |                                              |             |

| A1                        | 0.00                                                                |                                                                                         |                                                  |            |                  |           |               |             |                                              |             |

| L                         | 0.20                                                                |                                                                                         | ļ                                                |            |                  |           |               |             |                                              |             |

| k                         |                                                                     | 25 MIN.                                                                                 | 1                                                |            |                  |           |               |             |                                              |             |

| A2                        | 0.2                                                                 | 20 REF.                                                                                 | J                                                |            |                  |           |               |             |                                              |             |

|                           |                                                                     |                                                                                         |                                                  |            |                  |           |               |             |                                              |             |

| PACKAGE V                 | ARIATIONS                                                           | 3                                                                                       |                                                  |            |                  |           |               |             | 7                                            |             |

| PKG, CODE                 | N                                                                   | D2                                                                                      | E2                                               | е          | JEDEC SPEC       | ь         | [(N/2)-1] x e | DOWNBONDS   | 3                                            |             |

| T633-1                    | 6                                                                   | 1.50±0.10                                                                               | 2.30±0.10                                        | 0.95 BSC   | MO229 / WEEA     | 0.40±0.05 | 1.90 REF      | NO          | 7                                            |             |

| T633-2                    | 6                                                                   | 1.50±0.10                                                                               | 2.30±0.10                                        | 0.95 BSC   | MO229 / WEEA     | 0.40±0.05 | 1.90 REF      | NO          | 7                                            |             |

| T833-1                    | 8                                                                   | 1.50±0.10                                                                               | 2.30±0.10                                        | 0.65 BSC   | MO229 / WEEC     | 0.30±0.05 | 1.95 REF      | NO          | 7                                            |             |

| T833-2                    | 8                                                                   | 1.50±0.10                                                                               | 2.30±0.10                                        | 0.65 BSC   | MO229 / WEEC     | 0.30±0.05 | 1.95 REF      | NO          | 7                                            |             |

| T833-3                    | 8                                                                   | 1.50±0.10                                                                               | 2.30±0.10                                        | 0.65 BSC   | MO229 / WEEC     | 0.30±0.05 | 1.95 REF      | YES         | 7                                            |             |

| T1033-1                   | 10                                                                  | 1.50±0.10                                                                               | 2.30±0.10                                        | 0.50 BSC   | MO229 / WEED-3   | 0.25±0.05 | 2.00 REF      | NO          | 7                                            |             |

| T1433-1                   | 14                                                                  | 1.70±0.10                                                                               | 2.30±0.10                                        | 0.40 BSC   |                  | 0.20±0.05 | 2.40 REF      | YES         | 7                                            |             |

| T1433-2                   | 14                                                                  | 1.70±0.10                                                                               | 2.30±0.10                                        | 0.40 BSC   |                  | 0.20±0.05 | 2.40 REF      | NO          | 7                                            |             |

| 5. DRAWING                | RITY SHALL<br>SHALL NO<br>LENGTH/F<br>CHARACTE<br>CONFORM<br>33-1 & | NOT EXCED<br>T EXCEED<br>PACKAGE W<br>ERISTIC(S).<br>S TO JEDE<br>T1433-2.<br>NUMBER OF | ED 0.08 m<br>0.10 mm.<br>DTH ARE C<br>C MO229, I | onsidered  | ENSIONS "D2" ANI | ) "E2",   |               |             | /VI/J                                        | <b>(1</b> / |

| 6. "N" IS TH<br>7. NUMBER |                                                                     | SHOWN AF                                                                                | RE FOR REI                                       | FERENCE OI | NLY.             |           |               | TDFN, EXPOS | JTLINE, 6,8,10 & 14L,<br>SED PAD, 3x3x0.80 m |             |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.